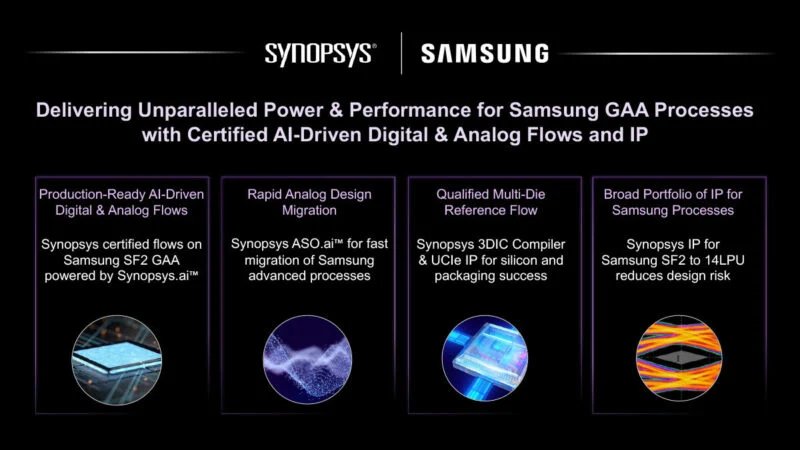

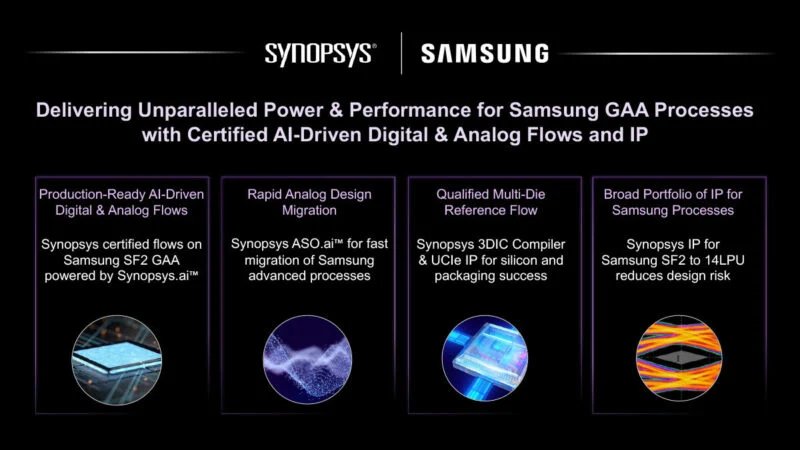

Synopsys ha anunciado que sus herramientas de proceso de diseño y su IP están listas para el proceso de fabricación de 2 nm en las fundiciones de Samsung Wafer.Samsung anunció recientemente que producirá chips de semiconductores de proceso de 2 nm en 2025 y declaró que el proceso mejorará aún más en 2027. La herramienta de diseño EDA de Synopsys ha aprobado la certificación de proceso GAA de 2NM de Samsung.

Según la introducción oficial, el kit EDA de Synopsys puede mejorar la migración de diseño de simulación, PPA (eficiencia de área, rendimiento y eficiencia energética) y la productividad de los nodos de proceso GAA de 2NM de Samsung Wafer Foundry Foundry.Synopsys utiliza la inteligencia artificial (IA) para la optimización colaborativa para ayudar a Samsung a mejorar la eficiencia del área, el rendimiento y la eficiencia energética del proceso de 2NM.

Las herramientas DSO.AI y ASO.AI de Synopsys se han migrado con éxito de Finfet a la arquitectura GAA, lo que significa que los clientes pueden migrar sin problemas sus diseños de chips Finfet existentes al nuevo proceso de 2NM GAA.

Las compañías de chips pueden usar herramientas de Synopsys para desarrollar nuevas tecnologías de diseño de chips, incluido el cableado de la fuente de alimentación trasera, los métodos de percepción del efecto de diseño local y el diseño de la unidad de nanoshois, mejorando así la eficiencia y el rendimiento de los procesos SF2.Samsung declaró que el nodo del proceso SF2Z puede mejorar aún más el rendimiento, el consumo de energía y la densidad (en un 20%).

Synopsys también reveló que su IP UCIE se ha utilizado en la producción de chips en los nodos de proceso Samsung SF2 y SF4X.Además, la misma solución DTCO también se utilizará para optimizar el nodo de proceso de 1,4 nm de Samsung (SF1.4).